# [Co/Tb]磁性細線の電流磁区駆動における熱酸化 Si 層厚の影響

奥田 光伸、川那 真弓、石井 紀彦、宮本 泰敬 (NHK 放送技術研究所)

Influence of Surface Oxidized Si Layer Thickness on Substrate for Current-driven Domain Wall Motion in [Co/Tb] Nanowire M. Okuda, M. Kawana, N. Ishii, Y. Miyamoto (NHK Science & Technology Research Labs.)

### はじめに

磁性細線における磁壁の電流駆動に関する研究 <sup>1)</sup>に注目が集まり、レーストラックメモリ <sup>2)</sup>に代表される新原理のメモリが提案されている。我々は磁性細線を並列に複数配置し、それらの磁区をパルス電流印加によって同期駆動する高速磁気記録デバイスの実現を目指して、磁性細線中の磁区を電流駆動する基礎研究を進めている <sup>3)</sup>。電流駆動時の磁区形状の変化を検証するため、磁気光学顕微鏡により[Co/Tb]磁性細線の磁区駆動を観察した。駆動電流量の増大に伴い磁区駆動速度は上昇するが、ある臨界を超えると発生したジュール熱により磁区の磁化状態が不安定になり、磁区が多数に分裂することで多磁区化することを確認した。そこで基板表面の熱酸化 Si 層に蓄積され磁区駆動を阻害するジュール熱の影響を検証するため、各熱酸化 Si 層厚条件におけるパルス電流を印加した際の磁性細線への影響を、磁気光学顕微鏡により観察したので報告する。

#### 実験方法

イオンビームスパッタ法および電子線リソグラフィーにより、 $Pt(3\ nm)/[Co(0.3nm)/Tb(0.6nm)]_s$  垂直磁化多層膜を表面熱酸化 Si 基板上に堆積して磁性細線を作製した。磁性細線の大きさは、幅  $5\ \mu m$ 、長さ  $20\ \mu m$  とした。パルス電流を印加するため、細線の両端に一対の電極を形成している。電流駆動実験には基板表面の絶縁性が求められるため、表面熱酸化 Si 層厚を  $20\sim400\ nm$  の範囲で変化させたものを用意し、それぞれの基板上に磁性細線を形成した。次に、パルス電流を印加して駆動実験に必要な初期磁区を導入した。細線長さ方向に  $500\ ns$  のパルス電流を印加して磁区が移動する様子を磁気光学顕微鏡により観察し、熱酸化 Si 層厚の違いによって磁区駆動速度や多磁区化する印加電流密度の変化について調査した。

## 実験結果

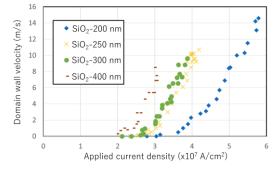

Fig.1 は Si 基板の表面熱酸化 Si 層厚を 200 ~ 400 nm の範囲で変化させた場合の、磁区駆動速度の印加電流密度依存性を示したものである。各熱酸化 Si 層厚条件において、磁区駆動可能な速度以上の駆動電流を印加した場合、初期磁区として導入した磁区は形状を保持できず多磁区化する様子が観察された。熱酸化 Si 層厚の減少に伴い、細線に印加できる電流密度の上限値が 3.0 x 10<sup>7</sup> A/cm² から 5.8 x 10<sup>7</sup> A/cm² へ上昇した結果、磁区駆動速度も 8.5 m/s から 14.6 m/s まで 6.1 m/s 上昇した。このとき、印加パルスの電流密度上限が 2.8 x 10<sup>7</sup> A/cm² 大きくなっているが、これは層厚の減少に対応して熱酸化 Si 層に蓄積可能な熱の総量が減少し、磁区

駆動の阻害要因が減少したためと考えられる。熱酸化 Si 層厚 200 nm と 400 nm の場合で多磁区化する際の電流密度を比較すると、500 ns のパルスを印加している間に発生するジュール熱の差分は  $1.6 \times 10^{-7}$  J と見積もられ、この熱の一部が熱酸化 Si 層に蓄積されているものと推測される。さらに薄い熱酸化 Si 層厚における磁区駆動の詳細についても当日報告する。

#### 参考文献

- 1) A. Yamaguchi et al.: Phys. Rev. Lett., 92, 077205 (2004).

- 2) S. S. P. Parkin et al.: Science, 320, 190 (2008).

- 3) M. Okuda et al.: IEEE Trans. Magn., 52, 7, 3401204 (2016).

Fig.1 Applied current density dependences of domain wall velocity for [Co/Tb] nanowires deposited on various SiO<sub>2</sub> surface oxidized layer thickness.